# **UDK3 Board Manager**

The Cesys UDK3 Board Manager is a tool to handle various management tasks with UDK3 compatible devices like FPGA design download and flash programming.

### **Introduction**

UDK3 Board Manager is a tool to perform generic tasks with UDK3 based devices. It can be used to:

- Display device data.

- · Download FPGA design to device.

- · Reset FPGA.

- Erase Flash memory.

- · Program Flash memory.

- Define User ID.

- · Convert FPGA designs to source files.

## FPGA design format

The file format for FPGA-Designs is .bin (not .bit !). With ISE, check option **Create** binary configuration file in **Programming File / Process Properties**.

To convert a .bit to .bin using the SDK, choose **Xilinx Tools / Launch Shell**. Change to the directory of the .bit and call **promgen -u 0 [design].bit -p bin -spi -w**, where **[design].bit** is the input file, and **[design].bin** is generated.

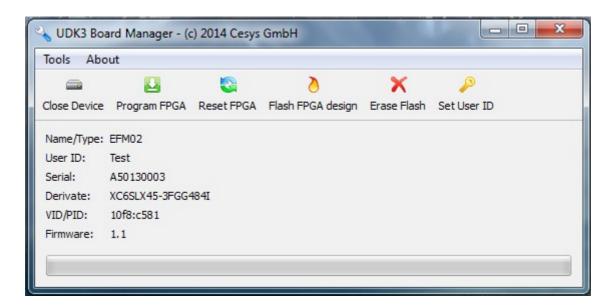

### **Main Screen**

The main screen shows information about the currently opened device and offers access to most functions through its toolbar.

To work with a Cesys FPGA board or module, use the mixed **Open Device** / **Close Device** button. If it shows the text **Close Device**, a device is currently opened. UDK3 Board Manager does **not** detect if the device is unplugged if it is opened.

Use **Program FPGA** to open a file dialog an to select a design file. The FPGA will be configured using the selected design.

**Reset FPGA** activates the dedicated reset I/O of the FPGA for some milliseconds.

**Flash FPGA design** shows a file selection dialog for FPGA bistreams. The flash memory must be erased before a new design can be programmed. The application will asks if erase should be done before downloading the design. A message box indicates the completion. Don't close the application or unplug the device during this process. Depending on the flash size, this process can take some minutes.

**Erase Flash** resets the flash to factory defaults. Don't close the application or unplug the device during this process. Depending on the flash size, this process can take some

minutes.

**Set User ID** let's input a short text that is written to the device EEPROM (not flash). This ID is useful to differentiate devices of the same type. This ID is accessible from the API as well.

#### Convert FPGA bitstreams to source code

This dialog is accessible from Tools menu, It generates source code from FPGA bitstreams. This is useful to embed bitstreams into your sources to compile them into a executable.

The code is created in the syntax of the language that is selected.

**Compress design** should always be enabled, this compresses the design using libz.

**Generate programming function** create a function or method that downloads the design. If this is not selected, only the design data is put into the source. Select FPGA design to convert opens a file dialog to choose the .bin file for conversion.

The name in the **Variable / Class name** field is used for variables in the source code. If **Use File name** is selected, the file name of the FPGA file is used instead. The name for the variable is not verified, choose a valid name.

After a design file is chosen, Copy to clipboard and Save to file are enabled.

## **Copyright Notice**

This file contains confidential and proprietary information of Cesys GmbH and is protected under international copyright and other intellectual property laws.

#### **Disclaimer**

This disclaimer is not a license and does not grant any rights to the materials distributed herewith. Except as otherwise provided in a valid license issued to you by Cesys, and to the maximum extent permitted by applicable law:

(1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND WITH ALL FAULTS, AND CESYS HEREBY DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE;

#### and

(2) Cesys shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under or in connection with these materials, including for any direct, or any indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Cesys had been advised of the possibility of the same.

#### **CRITICAL APPLICATIONS**

CESYS products are not designed or intended to be fail-safe, or for use in any application requiring fail-safe performance, such as life-support or safety devices or systems, Class III medical devices, nuclear facilities, applications related to the deployment of airbags, or any other applications that could lead to death, personal injury, or severe property or environmental damage (individually and collectively, "Critical Applications"). Customer assumes the sole risk and liability of any use of Cesys products in Critical Applications, subject only to applicable laws and regulations governing limitations on product liability.

THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS PART OF THIS FILE AT ALL TIMES.

CESYS Gesellschaft für angewandte Mikroelektronik mbH Zeppelinstrasse 6a D - 91074 Herzogenaurach Germany

# **Revision history**

| v1.0 | February, 17 2014 | Initial release.                |

|------|-------------------|---------------------------------|

| V1.1 | May, 13 2014      | Fpga .bin generation described. |

|      |                   |                                 |

# **Table of contents**

| <u>Introduction</u>                    | 2 |

|----------------------------------------|---|

| FPGA design format                     | 2 |

| Main Screen                            | 3 |

| Convert FPGA bitstreams to source code | 4 |

| Copyright Notice                       | 5 |

| Disclaimer                             | 5 |

| Revision history                       |   |