Embedded FPGA solutions

from cesys

We supply advanced off-the-shelf, customized and full custom FPGA modules and boards, developed by a seasoned, multidisciplinary team of FPGA experts.

Our modules have been developed to significantly reduce development time and cost to market. To achieve this goal, our product range includes not only the module, but also the necessary firmware, drivers and IP cores. Our goal is that our customers can fully concentrate on their development core task.

On request, we also offer development support for customer projects.

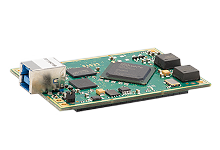

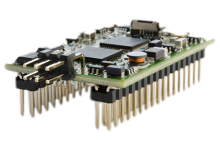

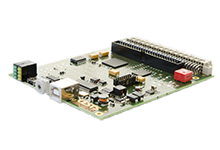

embedded FPGA boards & modules

All FPGA boards and modules include a UDK unified development kit license at no additional cost. UDK is available for Windows, Mac OS X and Linux.

For further Infomation please contact